Abstract

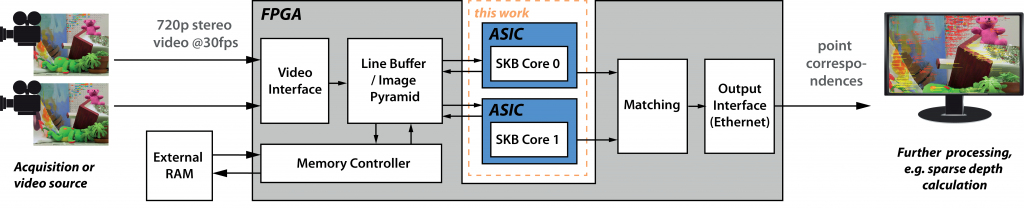

Several image processing applications rely on a sparse set of correspondence points between stereo images to discern a sparse but robust depth structure of the scene. There exist several methods to extract and match correspondences, but they are all computationally extensive and require significant memory bandwidths. In this paper, we describe an efficient ASIC core that is able to detect up to 25 k interest points in real time on a 720p video stream using the recently proposed Semantic Kernels Binarized (SKB) algorithm. To keep the memory bandwidth low, an optimized method to calculate the filter responses in the interest point detection stage has been devised. Instead of the 2D integral image, we use a local 1D integral image combined with an incremental updating scheme to calculate the box filters. The ASIC core is manufactured in 180nm technology and has a complexity of 254 kGE. It runs at 100 MHz, has a power dissipation of 184mW and is the central processing block for a larger FPGA based stereo vision system that calculates a sparse depth map by locating corresponding interest points between left and right images in real time.

Copyright Notice

The documents contained in these directories are included by the contributing authors as a means to ensure timely dissemination of scholarly and technical work on a non-commercial basis. Copyright and all rights therein are maintained by the authors or by other copyright holders, notwithstanding that they have offered their works here electronically. It is understood that all persons copying this information will adhere to the terms and constraints invoked by each author’s copyright. These works may not be reposted without the explicit permission of the copyright holder.