Abstract

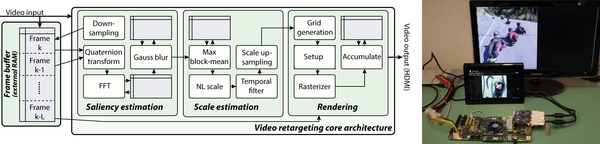

Aspect ratio retargeting for streaming video has actively been researched in the past years. While the mobile market with its huge diversity of screen formats is one of the most promising application areas, no existing algorithm is efficient enough to be embedded in such devices. In this work, we devise an efficient video retargeting algorithm by following an algorithm-architecture co-design approach, and we present the first FPGA implementation that is able to retarget full HD 1080p video at up to 60 frames per second. We furthermore show that our algorithm can be implemented on embedded processors at interactive framerates. Our hardware architecture only requires a modest amount of hardware resources and is portable to a dedicated ASIC for the use in consumer electronic devices such as displays or mobile phones.

Copyright Notice

The documents contained in these directories are included by the contributing authors as a means to ensure timely dissemination of scholarly and technical work on a non-commercial basis. Copyright and all rights therein are maintained by the authors or by other copyright holders, notwithstanding that they have offered their works here electronically. It is understood that all persons copying this information will adhere to the terms and constraints invoked by each author’s copyright. These works may not be reposted without the explicit permission of the copyright holder.